按一定的逻辑功能,把若干个门电路集成于一块芯片内,称为集成组合电路。内部可以采用不同的线路,但其外部输入输出的逻辑功能是相同的。邮政编码,电话号码,学生学号等都是采用了编码的知识。在数字电路中,一般采用二进制编码。二进制编码比较容易用电路来实现。

编码器

把0~9十个数码编成四位二进制代码的电路称为二——十进制编码器,采用8421码,其中8421称为每一位的权。按7字键(Y7),出现输出为0111,经过译码器翻译和数码管显示为7,松开按钮后7字消失,没有记忆功能。全加器

全加器进行两个二进制数的加法运算,是数字计算机的基本运算单位。

运算方法:

逢二进一。最低位只有两个数相加,无更低位的进位数称为半加。其余各位都有三个数相加,即被加数,加数和低位向本位的进位数。任何位相加的结果都有两个输出,一个是本位的和数,另一个是向高位的进位数。

实例

写出一位全加器的逻辑状态表,并根据逻辑状态表分别写出输出端(本位和数)(向高位的进位数)的逻辑式,最后根据逻辑式画出电路。用四个一位全加器实现四位加法器。

译码显示器

运用七段发光二极管组成的显示器,将计算机运算结果的二进制数翻译为人们易于理解的十进制数。运用高低电平组成的8421码和发光二极管组成的象形数字一一对应(七段译码器状态表)。把状态表写成逻辑式并简化,将上述逻辑关系增添试灯,灭灯等诸多功能,集成在一个芯片中,就成为七段译码器专用集成电路。16脚的7447七段译码器

4脚BI/RBO=0,灭灯。4脚BI/RBO=1,3脚LT=0时,亮灯显示8(全亮)。这两条用来测试显示是否正常。4脚BI/RBO=1,3脚LT=1,5脚RBI=0时,动态灭灯。(为了符合人们的习惯,多位数字显示时,有效数字前面的零和小数点后有效数字后面的零不应该显示,所以添加了动态灭灯的功能。)七段译码器输出与数码管输入应该按英文小写字母对应连接,并在连接处分别串一只100欧姆的限流电阻。

触发器

上述的组合逻辑电路重要的特征是输入信号改变,输出信号也随之改变。编码器用按钮输入信号时,松开按钮,信号便会消失。只能用开关输入信号,由于组合电路没有记忆功能,因而不能用按钮(脉冲)操作。触发器是具有记忆功能的逻辑电路,它的输出状态不仅与当时的输入有关,而且还有原来的输出状态有关,类似于人类的记忆功能。

基本RS触发器

把两个非门接成闭环,A门的输出回送到B门的输入,再把B的输出回送到A门的输入。两个门的输出总是互补的,两种输出状态都是稳定的,称为双稳态电路,这种电路具有记忆功能,电路的稳定状态取决于非门电源接通时刻的不可控制的随机因素。用有两个输入端的或非门代替非门,其中一个输入端接成闭环,另一个输入端作为信号端,这样就可以控制和改变电路的稳定状态。1、由或非门构成的RS触发器

S=1,R=0,此时B或非门有1出0,A门全0出1,以Q端状态为准,以高电平为有效信号,则称S端为置1端或者置位端。S=0,R=1,此时A门有1出0,Q=0,B门全0出1,称R端为置零端或者清零端。S=0,R=0,此时或非门的0信号是弃权信号,输出状态由其他输入端决定,输出状态保持原来状态。S=1,R=1,此时两个输出端全出0,输出端不再互补,这种输入方式客观存在但是不希望采用,使用约束条件(R与S=0)限制这种输入方式的出现,当两个信号同时撤除后R=S=0时,输出状态随机不定,容易引起电路误动作。

2、由与非门构成的RS触发器

S端为置位端,R端为置零端,低点平有效(逻辑符号图中输入端带有一个小圆圈),约束条件为R非与S非=1(R=S=0时候不满足条件)

实例:电冰箱温度控制电路、电动机正反转控制电路。

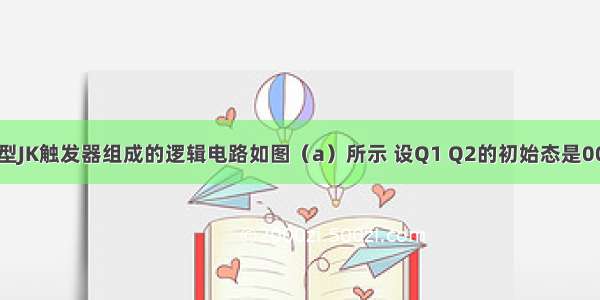

JK触发器(主从JK触发器)

它具有两个互补输出端和五个输入端。功能比rs触发器更丰富,克服了rs触发器需要人为地加约束和接成计数器时出现空翻现象。R、S分别称为清零端和置位端,低点平有效,加入互补信号,就可以设置输出端的状态。J、K称为驱动端,接受工作信号,不受约束,C端称为钟控端,加入时钟脉冲CP,时钟脉冲为0时,封锁J、K,不接收驱动信号,时钟脉冲为1时,J、K接受信号存于触发器内部,等下降沿到来时刻将信号反应到输出端上(后沿触发钟控端加一个小圆圈),要求J、K端信号在时钟脉冲为1的整段时间内不要改变。JK触发器增加钟控端功能,可使系统中多个触发器在同一时钟脉冲作用下同步输出。JK触发器的状态表和特性方程。

D触发器

它是具有两个互补输出端和四个输入端的触发器。RS分别是直接清零端和直接置位端,他们是低电平信号有效,不允许RS同时为零。D端是驱动端,接受工作信号。C端是前沿触发的钟控端。前沿触发即仅在CP时钟脉冲由低电平转到高电平时刻接收D信号,并立刻在Q端输出,其余时间CP=0或CP=1时均不接收D信号,输出状态保持不变。总结和实例

JK触发器驱动端悬空、D触发器Q非端与驱动端相连这两个电路在周期性的输入CP脉冲串的时候,输出信号都是不断的翻转,一个是后沿触发,一个是前沿出发。每个电路都可以作为二进制计数器,又称为二分频电路。两个电路都可以用一个按钮控制设备的启动和停止。并联多个相同的按钮可以实现多地控制一台设备的启动和停止。使用D触发器控制三台电动机顺序启动和停止(传送带控制),启动顺序ABC,停止顺序CBA,利用置位端和清零端作为反顺序操作的封锁。使用D触发器实现四人抢答电路。(74LS175数字芯片内含4个D触发器、一块7408芯片内含4个双端输入的与门)集成组合电路 编码器 全加器 译码显示器 RS触发器(或非门和与非门) 主从JK触发器 D触发器